Higher levels of integration have always played a critical role in advancing computing platforms of all types, lowering power, complexity and cost, while improving performance and efficiency. That said, an area of circuit design that perhaps hasn’t seen enough integration over the years, are clock timing solutions. However, that is going to change with the introduction of SiTime’s Chorus family of clock generators that are targeted at the quickly evolving AI data center and data center networking.

Clock timing circuits are a specialty support function of any modern device, server or workstation design. They are a heart beat of sorts for processors, driving core frequencies and keeping them in synchrony with data flow and other parts of the circuit. Historically, complex circuits have required multiple different types of timing products, like resonators and oscillators, to drive clock sources to buffers and generators for clock duplication, division and multiplication. With its recent acquisition of Aura Semiconductor, SiTime is now able to integrate all of these technologies into a single device, based on its MEMS resonator technology and Aura’s clock synthesis technologies.

SiTime Chorus Offers New-Found Levels Of Integration

Previously, at a high level, clock timing solutions looked like this, where each System on Chip device needs its own clock source…

High Level View Of Legacy Clock Timing Solution For A Compute Platform

Each instance of the “XO” represented here is a discrete timing solution driven by a crystal oscillator for each processor or IO device in an AI server application, for example.

With SiTime Chorus clock generators, that high level timing solution now looks like this…

SiTime Chorus Handling Clock Timing And Generation For Multiple Processors And Chips In A Compute

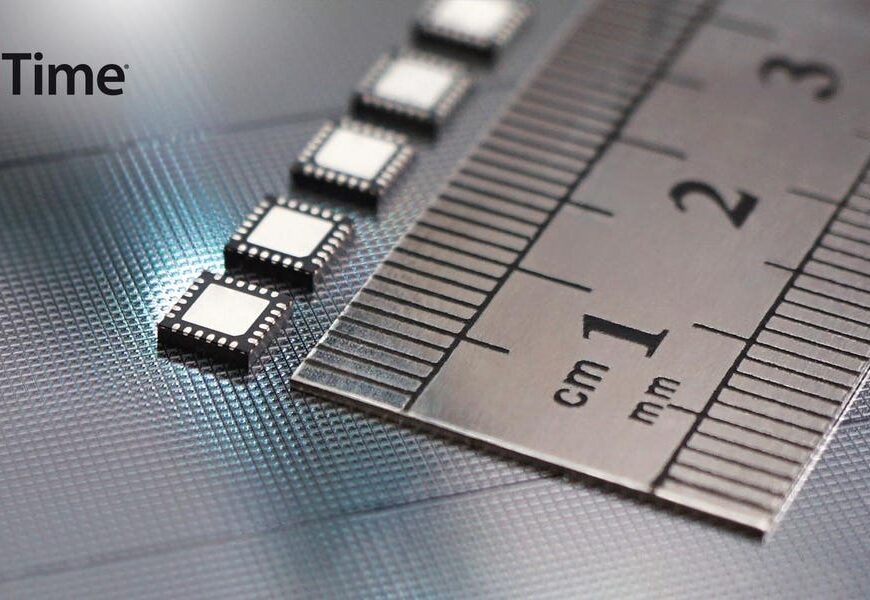

A picture is worth a thousand words, but as you can see, the complete timing solution for this simplified circuit design is now consolidated into a single SiTime Chorus clock generator, reducing board complexity and real estate, power consumption, and even multiple points of potential failure. SiTime claims Chorus also can deliver better performance with up to 10X better resilience, excellent stability and lower phase jitter (clock deviation), all in a single 4mm x 4mm package. It also vastly improves clock timing circuit design for engineers, such that the company notes Chorus clock generators can offer as much as a 6 week time-t0-market advantage.

Piyush Sevalia – SiTime executive vice president, marketing.

“AI is driving tremendous needs for higher data throughput in datacenters and lower power consumption, and SiTime is uniquely positioned to help address these issues,” said Piyush Sevalia, executive vice president of marketing at SiTime. “Before Chorus, hardware designers had to use discrete product types, such as clocks, oscillators and resonators, which resulted in performance compromises. Chorus delivers integrated clock generators to solve these problems and is yet another example of how we are transforming the timing market with our unique approach.”

SiTime is targeting Chorus towards key applications in the modern AI data center, like Smart NICs, PAM-4 400 – 800Gbps high speed communications links, and enterprise switching applications.

SiTime’s Chorus family of clock generators is sampling to strategic customers now, with general sampling availability in the second half of this year. All in, Chorus seems like a win-win for AI system design engineers that need precision timing solutions that are also greener, more reliable and ready-made for their applications.